(Electrostatic Discharge)是指具有不同静电电位的物体互相靠近或直接接触引起的电荷转移。

1、接触面广,活动范围大,很容易与带有静电荷的物体接触或摩擦而带电,同时也有许多机会将自身所带的电荷转移到器件上或者通过器件放电;

2、与大地之间的电容低,约为50一250pF,典型值为150PF,故少量的静电荷即可导致很高的静电势;

3、的电阻较低,相当于良导体,如手到脚之间的电阻只有几百欧姆,手指产生的接触电阻为几千至几十千欧姆,故处于静电场中也容易感应起电,而且某一部分带电即可造成全身带电。

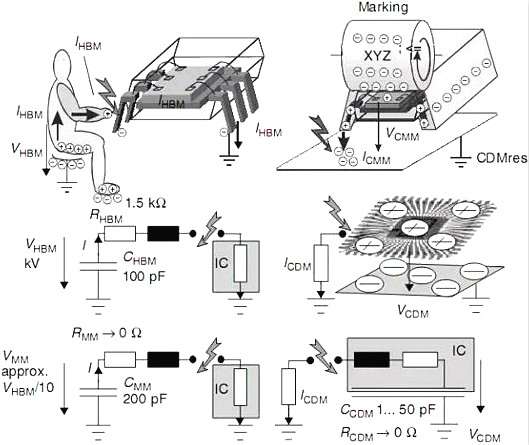

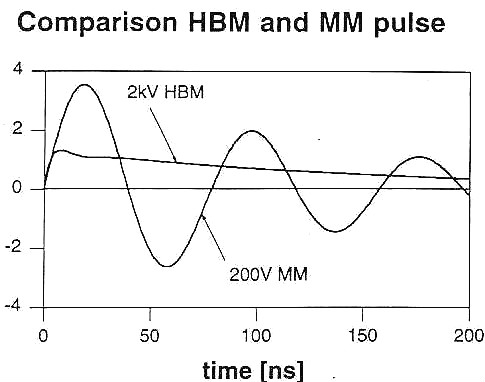

2、机器放电模式(MM):当然就是机器(如robot)移动产生的静电触碰芯片时由pin脚释放,次标准为EIAJ-IC-121 method 20(或者标准EIA/JESD22-A115-A),等效机器电阻为0 (因为金属),电容依旧为100pF。由于机器是金属且电阻为0,所以放电时间很短,几乎是ms或者us之间。但是更重要的问题是,由于等效电阻为0,所以电流很大,所以即使是200V的MM放电也比2kV的HBM放电的危害大。而且机器本身由于有很多导线互相会产生耦合作用,所以电流会随时间变化而干扰变化。

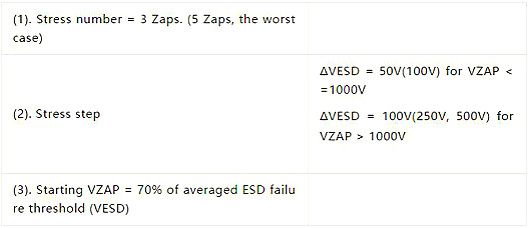

ESD的测试方法类似FAB里面的GOI测试,指定pin之后先给他一个ESD电压,持续一段时间后,然后再回来测试电性看看是否损坏,没问题再去加一个step的ESD电压再持续一段时间,再测电性,如此反复直至击穿,此时的击穿电压为ESD击穿的临界电压(ESD failure threshold Voltage)。通常我们都是给电路打三次电压(3 zaps),为了降低测试周期,通常起始电压用标准电压的70% ESD threshold,每个step可以根据需要自己调整50V或者100V。

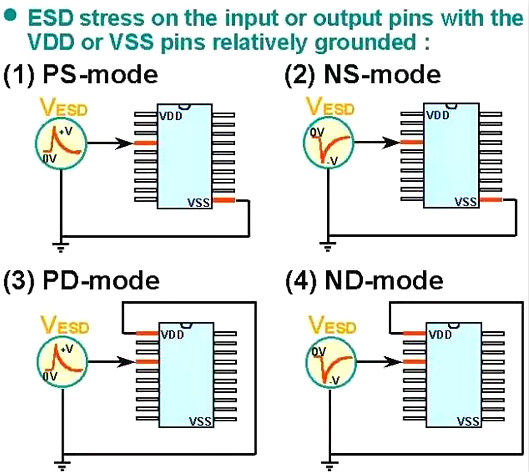

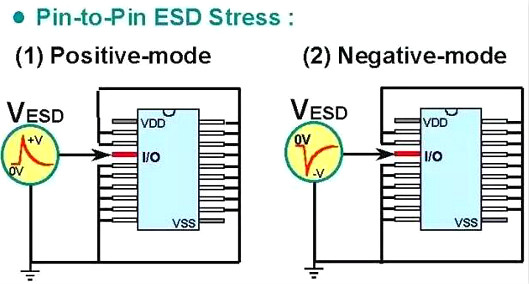

2. pin-to-pin测试:静电放电发生在pin-to-pin之间形成回路,但是如果要每每两个脚测试组合太多,因为任何的I/O给电压之后如果要对整个电路产生影响一定是先经过VDD/Vss才能对整个电路供电,所以改良版则用某一I/O-pin加正或负的ESD电压,其他所有I/O一起接地,但是输入和输出同时浮接(Floating)。

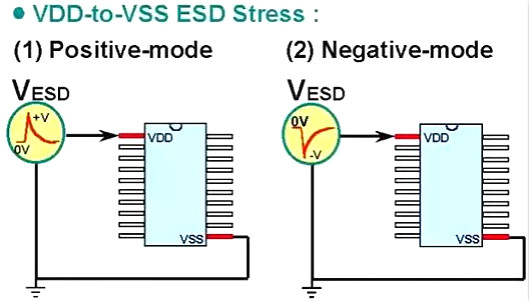

3、Vdd-Vss之间静电放电:只需要把Vdd和Vss接起来,所有的I/O全部浮接(floating),这样给静电让他穿过Vdd与Vss之间。

4、Analog-pin放电测试:因为模拟电路很多差分比对(Differential Pair)或者运算放大器(OP AMP)都是有两个输入端的,防止一个损坏导致差分比对或运算失效,所以需要单独做ESD测试,当然就是只针对这两个pin,其他pin全部浮接(floating)。

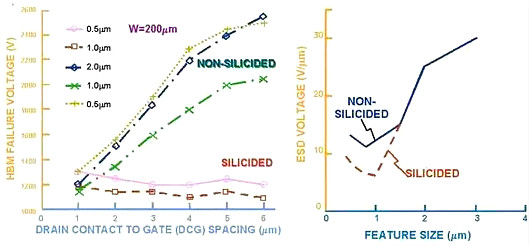

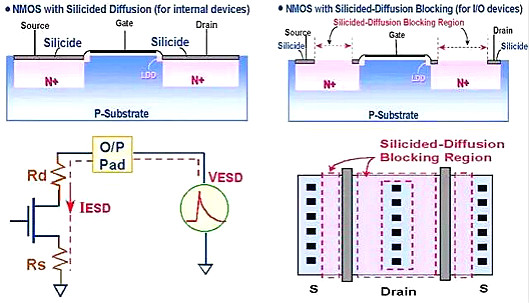

随着摩尔定律的进一步缩小,器件尺寸越来越小,结深越来越浅,GOX越来越薄,所以静电击穿越来越容易,而且在Advance制程里面,Silicide引入也会让静电击穿变得更加尖锐,所以几乎所有的芯片设计都要克服静电击穿问题。

静电放电保护可以从FAB端的Process解决,也可以从IC设计端的Layout来设计,所以你会看到Prcess有一个ESD的option layer,或者Design rule里面有ESD的设计规则可供客户选择等等。当然有些客户也会自己根据SPICE model的电性通过layout来设计ESD。

1、制程上的ESD:要么改变PN结,要么改变PN结的负载电阻,而改变PN结只能靠ESD_IMP了,而改变与PN结的负载电阻,就是用non-silicide或者串联电阻的方法了。

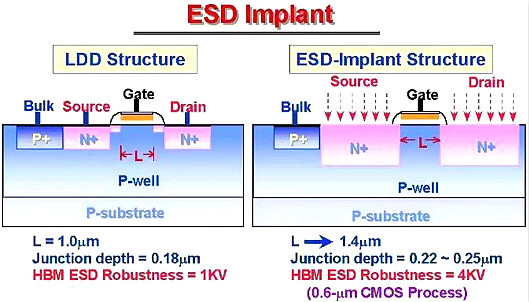

1) Source/Drain的ESD implant:因为我们的LDD结构在gate poly两边很容易形成两个浅结,而这个浅结的尖角电场比较集中,而且因为是浅结,所以它与Gate比较近,所以受Gate的末端电场影响比较大,所以这样的LDD尖角在耐ESD放电的能力是比较差的(1kV),所以如果这样的Device用在I/O端口,很容造成ESD损伤。所以根据这个理论,我们需要一个单独的器件没有LDD,但是需要另外一道ESD implant,打一个比较深的N+_S/D,这样就可以让那个尖角变圆而且离表面很远,所以可以明显提高ESD击穿能力(4kV)。但是这样的话这个额外的MOS的Gate就必须很长防止穿通(punchthrough),而且因为器件不一样了,所以需要单独提取器件的SPICE Model。

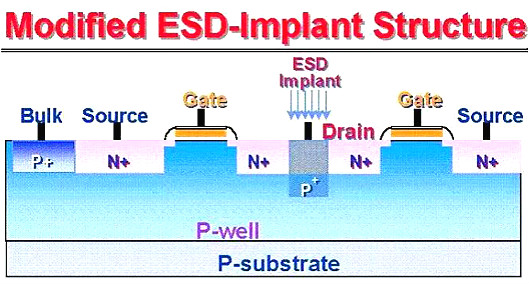

2) 接触孔(contact)的ESD implant:在LDD器件的N+漏极的孔下面打一个P+的硼,而且深度要超过N+漏极(drain)的深度,这样就可以让原来Drain的击穿电压降低(8V--6V),所以可以在LDD尖角发生击穿之前先从Drain击穿导走从而保护Drain和Gate的击穿。所以这样的设计能够保持器件尺寸不变,且MOS结构没有改变,故不需要重新提取SPICE model。当然这种智能用于non-silicide制程,否则contact你也打不进去implant。

4)串联电阻法:这种方法不用增加光罩,应该是最省钱的了,原理有点类似第三种(SAB)增加电阻法,我就故意给他串联一个电阻(比如Rs_NW,或者HiR,等),这样也达到了SAB的方法。

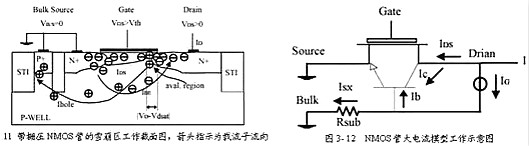

以NMOS为例,原理都是Gate关闭状态,Source/Bulk的PN结本来是短接0偏的,当I/O端有大电压时,则Drain/Bulk PN结雪崩击穿,瞬间bulk有大电流与衬底电阻形成压差导致Bulk/Source的PN正偏,所以这个MOS的寄生横向NPN管进入放大区(发射结正偏,集电结反偏),所以呈现Snap-Back特性,起到保护作用。PMOS同理推导。

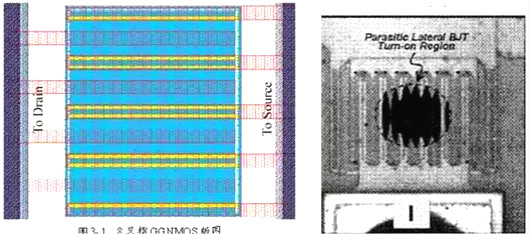

如何触发?必须有足够大的衬底电流,所以后来发展到了现在普遍采用的多指交叉并联结构(multi-finger)。但是这种结构主要技术问题是基区宽度增加,放大系数减小,所以Snap-back不容易开启。而且随着finger数量增多,会导致每个finger之间的均匀开启变得很困难,这也是ESD设计的瓶颈所在。

在将电缆移去或连接到网络分析仪上时,防止静电放电(ESD)是十分重要的。静电可以在您的身体上形成且在放电时很容易损坏灵敏的内部电路元件。一次太小以致不能感觉出的静电放电可能造成永久性损坏。

4、半导体器件应盛放在防静电塑料盛器或防静电塑料袋中, 这种防静电盛器有良好导电性能, 能有效防止静电的产生。当然, 有条件的应盛放在金属盛器内或用金属箔包装。